## OVERVIEW

The SM9501A is a BiCMOS RCC<sup>\*1</sup> receiver IC. It accepts low frequency standard wave input received from an external antenna, amplifies it, detects the data signal, and outputs a digital time code signal.

\*<sup>1</sup>: Radio controlled clock

## FEATURES

- Operating supply voltage range: 2.4 to 3.6V

- Operating current consumption: 55 $\mu$ A (typ) @3V

- Standby current consumption: 0.1 $\mu$ A (max) @3V

- High sensitivity: 0.5 $\mu$ Vrms input

- Wide frequency range (35kHz to 80kHz)

- Include analog switch for antennatuning capacitors change

- AGC gain hold function

- External crystal filter connection

- BiCMOS process

- Package:16-pin VSOP, Chip form

## ORDERING INFORMATION

| Device   | Package     |

|----------|-------------|

| SM9501AV | 16-pin VSOP |

| CF9501A  | Chip form   |

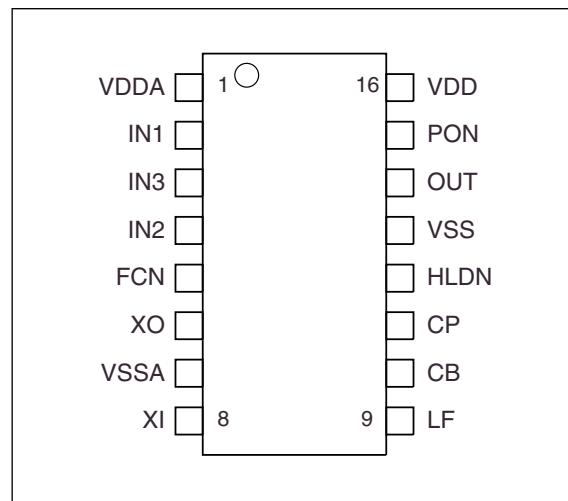

## PINOUT

(Top view)

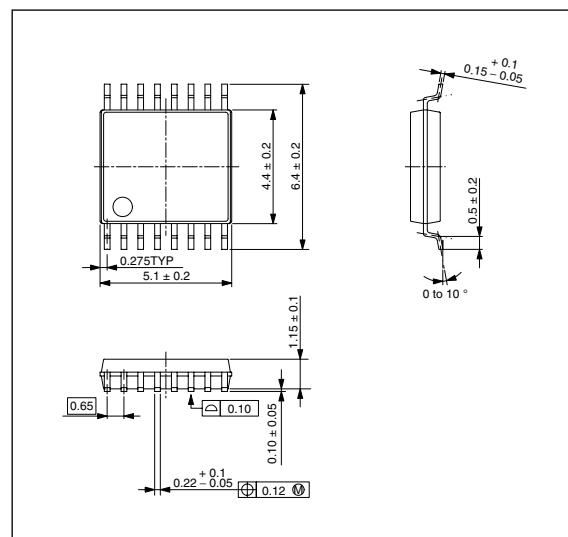

## PACKAGE DIMENSIONS

(Unit: mm)

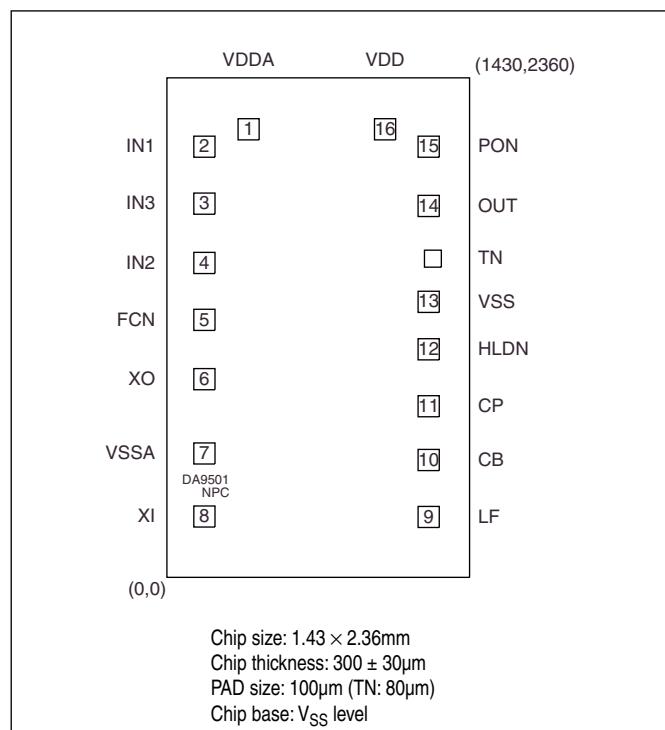

**PAD LAYOUT (CF9501A)**(Unit:  $\mu\text{m}$ )**PAD NAME and DIMENSIONS (CF9501A)**

| Pad number | Pad name        | Pad dimensions [ $\mu\text{m}$ ] |      |

|------------|-----------------|----------------------------------|------|

|            |                 | X                                | Y    |

| 1          | VDDA            | 386                              | 2117 |

| 2          | IN1             | 177                              | 2035 |

| 3          | IN3             | 177                              | 1766 |

| 4          | IN2             | 177                              | 1486 |

| 5          | FCN             | 177                              | 1217 |

| 6          | XO              | 177                              | 937  |

| 7          | VSSA            | 177                              | 586  |

| 8          | XI              | 177                              | 288  |

| 9          | LF              | 1237                             | 286  |

| 10         | CB              | 1237                             | 555  |

| 11         | CP              | 1237                             | 809  |

| 12         | HLDN            | 1237                             | 1078 |

| 13         | VSS             | 1237                             | 1302 |

| 14         | OUT             | 1237                             | 1755 |

| 15         | PON             | 1237                             | 2035 |

| 16         | VDD             | 1031                             | 2117 |

| —          | TN <sup>1</sup> | 1257                             | 1506 |

1. For test mode

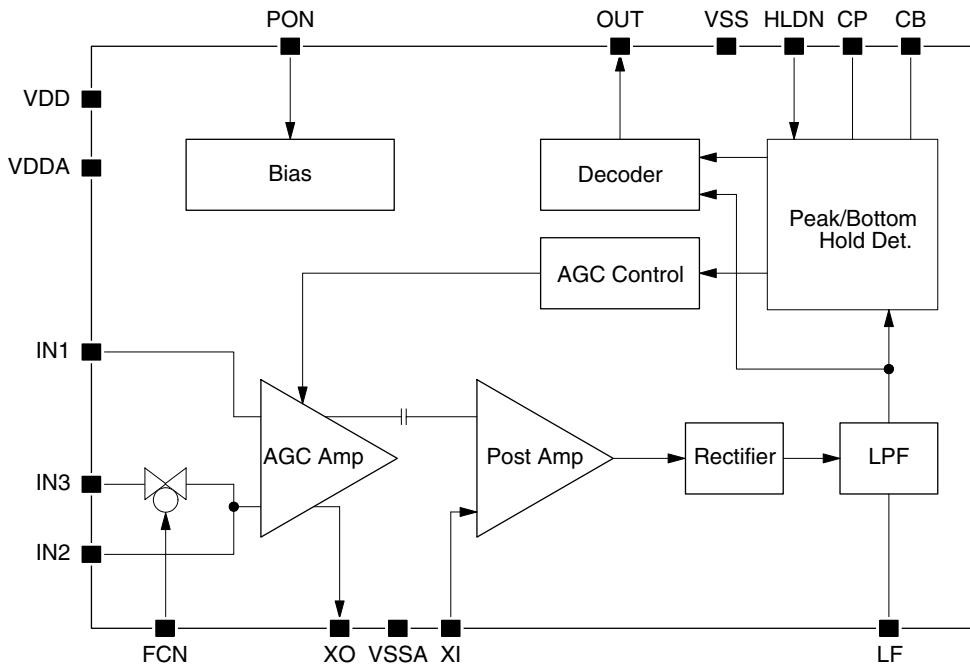

## BLOCK DIAGRAM

## PIN DESCRIPTION

| Number | Name | I/O <sup>1</sup> | A/D <sup>2</sup> | Description                                                   |

|--------|------|------------------|------------------|---------------------------------------------------------------|

| 1      | VDDA | —                | A                | AGC amplifier (+) supply input                                |

| 2      | IN1  | I                | A                | Antenna input 1 (fixed input)                                 |

| 3      | IN3  | I                | A                | Antenna input 3 (via analog switch)                           |

| 4      | IN2  | I                | A                | Antenna input 2 (analog switch bypass)                        |

| 5      | FCN  | Ipu              | D                | Analog switch control input (active LOW)                      |

| 6      | XO   | O                | A                | Output for crystal filter                                     |

| 7      | VSSA | —                | A                | AGC amplifier (−) supply input                                |

| 8      | XI   | I                | A                | Input from crystal filter                                     |

| 9      | LF   | O                | A                | Rectifier LPF capacitor connection                            |

| 10     | CB   | O                | A                | Bottom hold detector capacitor connection                     |

| 11     | CP   | O                | A                | Peak hold detector capacitor connection                       |

| 12     | HLDN | Ipu              | D                | AGC gain hold control (active LOW)                            |

| 13     | VSS  | —                | A                | Substrate (−) supply input                                    |

| 14     | OUT  | O                | D                | Clock time code output (active LOW)                           |

| 15     | PON  | Ipu              | D                | Standby state control input (active LOW)                      |

| 16     | VDD  | —                | A                | (+) supply input                                              |

| —      | TN   | Ipu              | D                | AGC amplifier gain control switch (active LOW, for test mode) |

1. I: input, O: output, Ipu: input with pull-up resistor, -: supply pin

1. I: input, O: output, Ipu: input with

2. A: analog signal, D: digital signal

## SPECIFICATIONS

### Absolute Maximum Ratings

$V_{SS} = 0V$

| Parameter                 | Symbol    | Condition   | Rating                | Unit |

|---------------------------|-----------|-------------|-----------------------|------|

| Supply voltage range      | $V_{DD}$  |             | −0.3 to +7.0          | V    |

| Input voltage range       | $V_{IN}$  |             | −0.3 to $V_{DD}$ +0.3 | V    |

| Power dissipation         | $P_D$     | 16-pin VSOP | 150                   | mW   |

| Storage temperature range | $T_{stg}$ | 16-pin VSOP | −55 to +125           | °C   |

|                           |           | Chip form   | −65 to +150           | °C   |

Note. Absolute maximum ratings are the values that must never exceed even for a moment. The device may be damaged or deteriorated the characteristics or reliability if these parameter ratings are exceeded.

### Recommended Operating Conditions

$V_{SS} = 0V$

| Parameter                   | Symbol    | Condition | Rating     | Unit |

|-----------------------------|-----------|-----------|------------|------|

| Supply voltage range        | $V_{DD}$  |           | 2.4 to 3.6 | V    |

| Operating temperature range | $T_{opr}$ |           | −20 to +70 | °C   |

## Electrical Characteristics

$V_{DD} = 2.4$  to  $3.6V$ ,  $V_{SS} = 0V$ ,  $T_a = -20$  to  $+70^{\circ}C$  unless otherwise noted.

| Parameter                                          | Symbol     | Condition                                                                                                                           | Rating       |      |      | Unit          |

|----------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|---------------|

|                                                    |            |                                                                                                                                     | min          | typ  | max  |               |

| Supply voltage                                     | $V_{DD}$   |                                                                                                                                     | 2.4          | 3.0  | 3.6  | V             |

| Maximum operating current consumption <sup>1</sup> | $I_{DDM}$  | $V_{DD} = 3.0V$ , $T_a = 25^{\circ}C$ , no input signal, PON: VSS, OUT: no load                                                     | —            | 65   | 100  | $\mu A$       |

| Operating current consumption <sup>1</sup>         | $I_{DDT}$  | $V_{DD} = 3.0V$ , $T_a = 25^{\circ}C$ , 0.1mVrms input amplitude (differential input), 500ms pulsewidth, PON: VSS, OUT: no load     | —            | 55   | —    | $\mu A$       |

| Standby mode current consumption                   | $I_{ST}$   | $V_{DD} = V_{DDA} = 3.6V$ , PON, FCN, HLDN: OPEN, OUT: no load                                                                      | —            | —    | 0.1  | $\mu A$       |

| Minimum input voltage range                        | $V_{fmin}$ | IN1-IN2 differential input, $f_{IN} = 40kHz$ , $60kHz$ , $T_a = 25^{\circ}C$                                                        | —            | 0.5  | 1.0  | $\mu V_{rms}$ |

| Maximum input voltage range                        | $V_{fmax}$ | IN1-IN2 differential input, $f_{IN} = 40kHz$ , $60kHz$                                                                              | 80           | —    | —    | $mV_{rms}$    |

| Input frequency                                    | $f_{IN}$   | IN1-IN2 differential input                                                                                                          | 35           | —    | 80   | kHz           |

| Analog switch resistance                           | $R_A$      | $V_{IN2} = 0V$ , $V_{IN3} = 50mV$                                                                                                   | —            | —    | 15   | $\Omega$      |

| Startup time <sup>2</sup>                          | $t_{ON}$   | When supply is applied                                                                                                              | —            | —    | 8    | sec           |

| Startup time <sup>2</sup> (PON)                    | $t_{PON}$  | From standby mode                                                                                                                   | —            | —    | 8    | sec           |

| Input voltage                                      | $V_{IL}$   | PON, FCN, HLDN pins                                                                                                                 | —            | —    | 0.5  | V             |

|                                                    | $V_{IH}$   |                                                                                                                                     | $V_{DD}-0.5$ | —    | —    | V             |

| Input current                                      | $I_{IL}$   | $V_{IL} = 0V$ , PON, FCN, HLDN pins                                                                                                 | —            | -0.5 | -1.5 | $\mu A$       |

|                                                    | $I_{IH}$   | $V_{IH} = V_{DD}$ , PON, FCN, HLDN pins                                                                                             | —            | —    | 1    | $\mu A$       |

| LOW-level output current                           | $I_{OL}$   | OUT pin, $V_{OL} = V_{SS} + 0.5V$                                                                                                   | 10           | —    | —    | $\mu A$       |

| HIGH-level output current                          | $I_{OH}$   | OUT pin, $V_{OH} = V_{DD} - 0.5V$                                                                                                   | -10          | —    | —    | $\mu A$       |

| Gain hold time                                     | $t_{HLD}$  | $\pm 3dB$ change                                                                                                                    | 1            | —    | —    | sec           |

| Fall time output propagation delay <sup>3</sup>    | $t_{DN}$   | $f_{IN} = 40kHz$ , $60kHz$ , $T_a = 25^{\circ}C$ , $V_{IN} = 1\mu V_{rms}$ to $80mV_{rms}$ , NPC standard crystal, NPC standard jig | —            | —    | 160  | ms            |

| Rise time output propagation delay <sup>3</sup>    | $t_{UP}$   |                                                                                                                                     | —            | —    | 200  | ms            |

| LOW-level output pulsewidth <sup>4</sup> (200ms)   | $T_{200}$  |                                                                                                                                     | 100          | 200  | 300  | ms            |

| LOW-level output pulsewidth <sup>4</sup> (500ms)   | $T_{500}$  |                                                                                                                                     | 400          | 500  | 650  | ms            |

| LOW-level output pulsewidth <sup>4</sup> (800ms)   | $T_{800}$  |                                                                                                                                     | 700          | 800  | 900  | ms            |

| Noise rejection ratio <sup>5</sup>                 | S/N        |                                                                                                                                     | —            | —    | 9    | dB            |

1. Measured using the standard circuit.

2. The time taken under stable wave input conditions from when power is applied or standby is released, using PON, until stable digital output occurs within ratings.

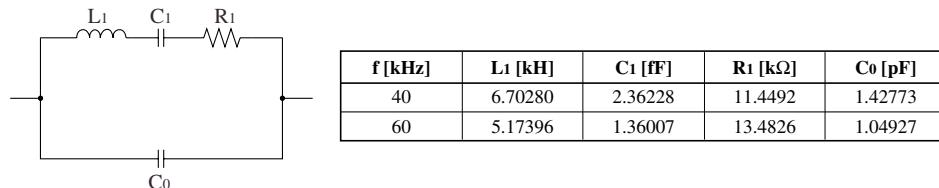

3. The time taken, with 10:1 input signal amplitude ratio and 500ms pulsewidth, from when a change in signal input amplitude occurs until the output OUT changes. Note that this characteristic is very dependent on the antenna and crystal filter characteristics. The standard crystal used for crystal filter by our measurement has the following equivalent circuit coefficients as reference values.

4. Values obtained when using the crystal filter employed here. Note that these values are dependent on the crystal characteristics, and should be considered as reference values.

5. Time averaged rms values, where the noise is white noise and the measurement bandwidth is determined by the crystal filter equivalent used in the standard circuit. Note that this value is very dependent on the crystal filter characteristics used.

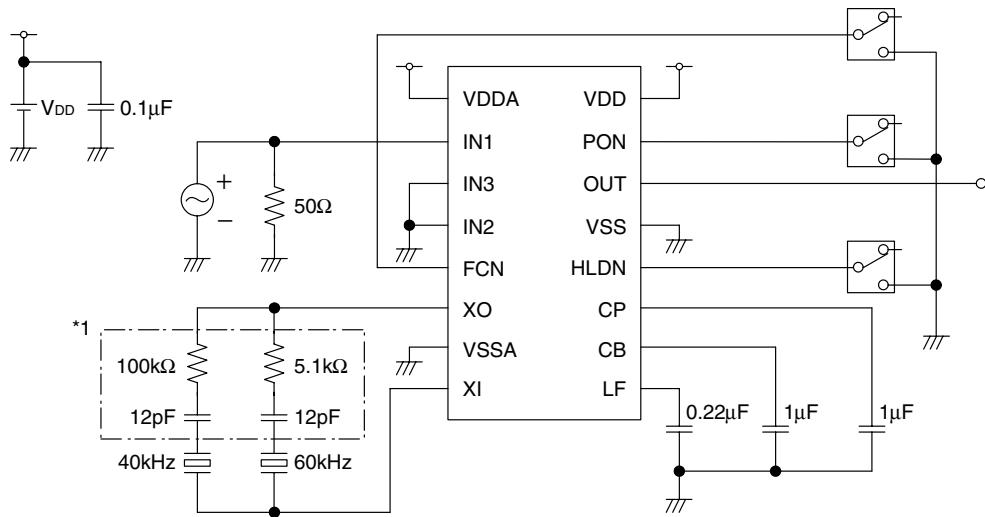

## STANDARD CIRCUIT

\*1. These values are obtained when using NPC's standard crystal and should be considered as reference values.

In case of using different crystal, the values are different.

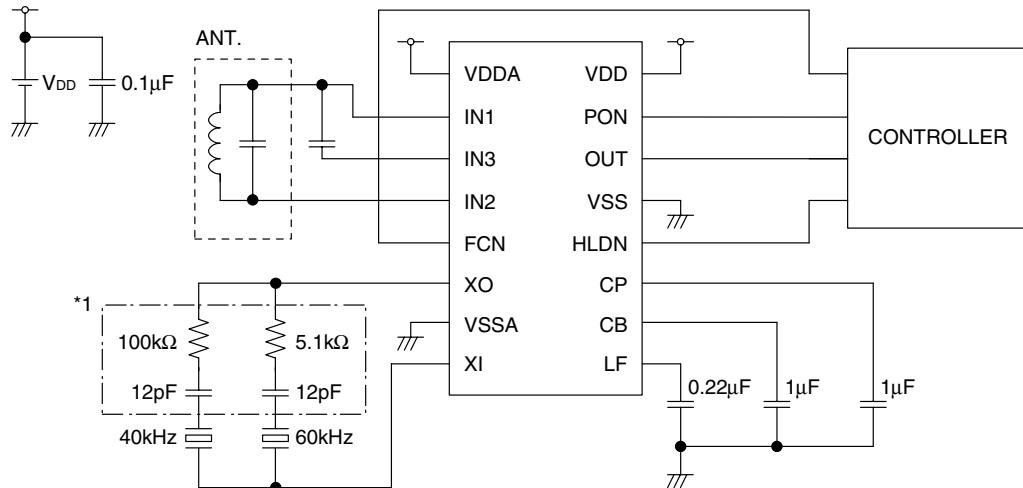

## APPLICATION CIRCUIT

\*1. These values are obtained when using NPC's standard crystal and should be considered as reference values.

In case of using different crystal, the values are different.

## FUNCTIONAL DESCRIPTION

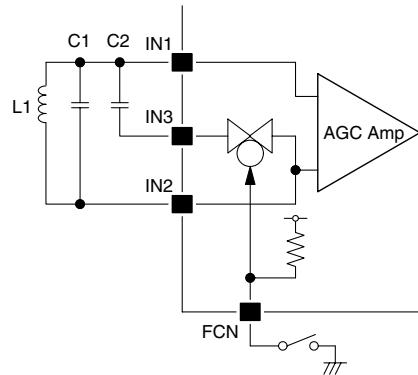

### Antenna Input and Tuning Capacitor Switching Function

There are three antenna inputs: IN1, IN2, and IN3. When FCN is open (or HIGH), the internal analog switch is OFF and IN1–IN2 are the antenna inputs (60kHz mode). When FCN is LOW, the analog switch is ON, connecting IN3 and IN2. C2 is then connected in parallel to C1 in the tuning circuit, reducing the resonant frequency (40kHz mode).

| FCN          | Analog switch | Antenna input            | Tuning capacitor | Receiver frequency |

|--------------|---------------|--------------------------|------------------|--------------------|

| Open or HIGH | OFF           | Between IN1 and IN2      | C1               | 60kHz              |

| LOW          | ON            | Between IN1 and IN2, IN3 | C1 + C2 parallel | 40kHz              |

FCN should be left open if not using the tuning capacitor switching function, and IN2 should be connected to IN3 externally.

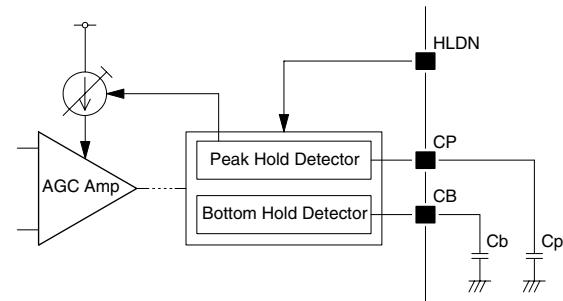

### AGC Amplifier and Gain Hold Function

The input voltage from the antenna is amplified by the AGC amplifier. The gain can be monitored by the voltage on pin CP, and can be changed by varying the CP voltage. An external capacitor Cp can be connected to CP to stabilize the voltage, but the gain tracking time is dependent on the capacitance. When HLDN is open (or HIGH), the gain automatically adjusts to follow the post-amplifier detector signal. When HLDN is LOW, the immediately preceding gain is held for an interval determined by the Cp capacitance.

| HLDN         | Gain tracking   |

|--------------|-----------------|

| Open or HIGH | Auto tracking   |

| LOW          | Gain held fixed |

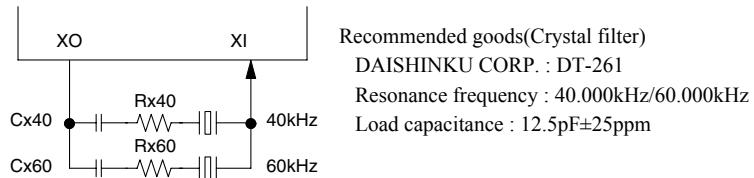

## Crystal Filter Circuit

External crystals are used as filters. Multiple frequencies (40kHz and 60kHz) are supported by connecting crystals in parallel. The center frequency and bandwidth of the filters is determined by the crystal characteristics. If the center frequency is lower than the target frequency, C<sub>x</sub>40 and C<sub>x</sub>60 can be added to change the resonant frequency. And Rx40 and Rx60 can be added to adjust the filter Q factor. Internally, pin XO is linked to pin XI by a phase-inverted signal passed through a capacitor, which cancels the high-frequency components that pass through the crystal parallel capacitances.

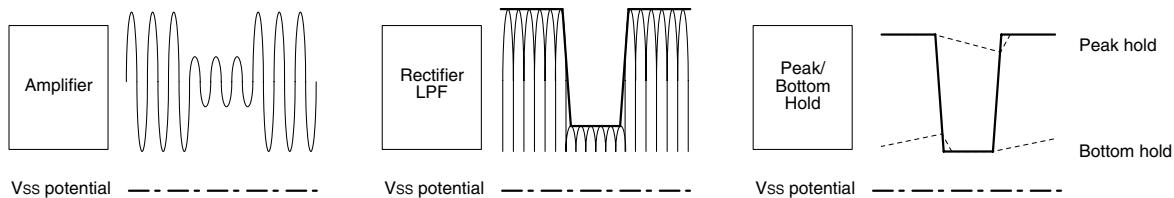

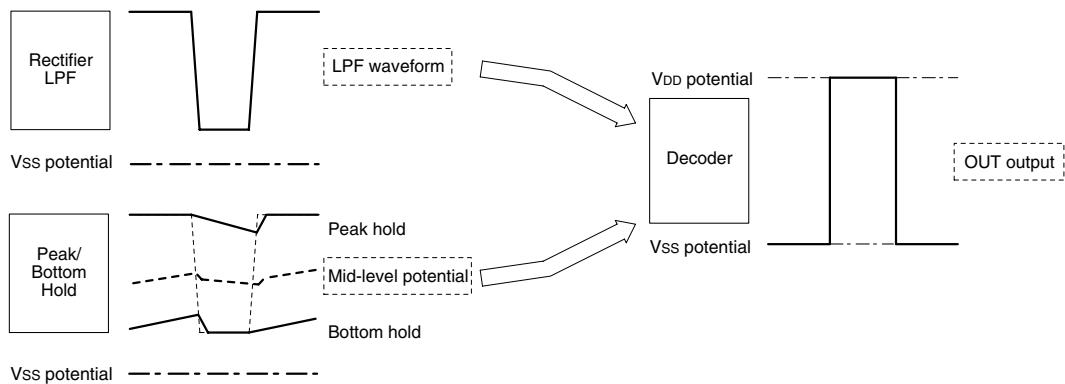

## Detector Circuit

The amplified signal is full-wave rectified and passed through a lowpass filter detector. The detector output is input to peak hold (pin CP) and bottom hold (pin CB) circuits to form the decoder reference potentials and peak hold potential for AGC control.

## Decoder Circuit

The detector output and peak/bottom hold mid-level potential reference are used to decode the time code signal, which is output on pin OUT. The output is active-LOW, so that the output is LOW when the input amplitude is HIGH.

## Standby Function

When PON is open (or HIGH), the device is in standby mode and the current consumption is reduced. Receiver operation starts when PON goes LOW.

| PON            | Mode      | OUT       |

|----------------|-----------|-----------|

| Open (or HIGH) | Standby   | HIGH      |

| LOW            | Operating | Time code |

Please pay your attention to the following points at time of using the products shown in this document.

1. The products shown in this document (hereinafter "Products") are designed and manufactured to the generally accepted standards of reliability as expected for use in general electronic and electrical equipment, such as personal equipment, machine tools and measurement equipment. The Products are not designed and manufactured to be used in any other special equipment requiring extremely high level of reliability and safety, such as aerospace equipment, nuclear power control equipment, medical equipment, transportation equipment, disaster prevention equipment, security equipment. The Products are not designed and manufactured to be used for the apparatus that exerts harmful influence on the human lives due to the defects, failure or malfunction of the Products. If you wish to use the Products in that apparatus, please contact our sales section in advance. In the event that the Products are used in such apparatus without our prior approval, we assume no responsibility whatsoever for any damages resulting from the use of that apparatus.

2. NPC reserves the right to change the specifications of the Products in order to improve the characteristics or reliability thereof.

3. The information described in this document is presented only as a guide for using the Products. No responsibility is assumed by us for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of the third parties. Then, we assume no responsibility whatsoever for any damages resulting from that infringements.

4. The constant of each circuit shown in this document is described as an example, and it is not guaranteed about its value of the mass-production products.

5. In the case of that the Products in this document falls under the foreign exchange and foreign trade control law or other applicable laws and regulations, approval of the export to be based on those laws and regulations are necessary. Customers are requested appropriately take steps to obtain required permissions or approvals from appropriate government agencies.

SEIKO NPC CORPORATION

1-9-9, Hatchobori, Chuo-ku,

Tokyo 104-0032, Japan

Telephone: +81-3-5541-6501

Facsimile: +81-3-5541-6510

<http://www.npc.co.jp/>

Email: [sales@npc.co.jp](mailto:sales@npc.co.jp)